# A CEA Tech institute partnership between List and Leti

# Advanced research drives business growth

CEA Tech, France's national technology research organization, was established to bridge the gap between basic scientific research and the transfer of new technologies to industry. Together, CEA Tech's three institutes—Leti. Liten. and List—develop a broad portfolio of technologies for ICTs, energy, and healthcare. CEA Tech leverages a unique innovation-driven culture to provide businesses with access to the advanced technologies they need to get ahead of the competition.

### Toward greater data security, smaller form factors, and higher energy efficiency

Information processing technologies and communications systems are everywhere: in our mobile devices, household appliances, cars, portable medical devices, and more. These technologies and systems will drive the widespread development of emerging trends like the Internet of Things (IoT), Smart Cities, Autonomous Vehicles, and Smart Manufacturing—helping billions of objects around the world to connect securely and efficiently.

# Combining research in hardware and software design

Today's technology challenges require a holistic approach to hardware and software. CEA Tech institute Leti brings advanced know-how in integrated circuit design and testing, while List has built up renowned expertise in embedded software development. Together, the two institutes are poised to address the challenges of the future

### Unique in Europe

CEA Tech is Europe's first research organization to offer a comprehensive range of R&D services for businesses, giving its partners a single point of access to all of the know-how and technologies required to develop smart, integrated embedded systems.

The rise of the IoT has brought with it the need to design novel smart devices capable of computing and communicating locally with extreme energy efficiency while also generating huge amounts of data in the cloud that require extensive storage and processing capacity in high performance servers. Real-time performance, fast data processing, low energy consumption, security, and reliability are critical for IoT applications, from devices to infrastructures.

Read on to learn about how CEA Tech is addressing computing, wireless communications, smart sensors, imagers, and system reliability. Our philosophy and vision are unique, as evidenced by the innovations you will discover on the following pages.

CEA Tech designs are validated on silicon or at system level before being integrated into demonstrators. Our facilities in Grenoble (on the MINATEC campus) and in Paris-Saclay are open to visitors offering you an opportunity to see first-hand how CEA Tech is paving the way for advances in areas such as artificial intelligence and autonomous systems.

We hope will you enjoy reading this overview of our activities.

Thierry Collette, VP Division Architecture & IC Design, Embedded Software

# Three emerging trends and a common challenge

The demand for information processing—driven by the Internet of Things, Autonomous Vehicles, and Smart Manufacturing—is growing at an unprecedented pace. Idate Digiworld forecasts that by 2020 over 80 billion connected devices will be active worldwide. Cisco estimates that this will generate IP traffic of ten billion billion bytes each day, an amount of data that would require a 1,000-km-high stack of DVDs of storage. Therefore, the key challenges for infrastructure and terminal nodes are:

Integration of flexible processing power with energy efficiency and operational safety and security

# Internet of Things

The potential uses for connected devices are virtually endless, spanning healthcare, energy, environmental monitoring, transportation, smart buildings and cities, farming, law enforcement, and more. These devices must be able to sense, record, process, transmit, and receive pertinent information. They must also be extremely energy-efficient. The IoT will leverage Big Data through a network of high-performance servers and micro-servers. Manufactured by a multitude of different companies, connected devices will form a vast but heterogeneous network in need of interoperability, configurability, access regulation, and fault management. Software tools to manage and safely and securely access the IoT network will become critical differentiators.

# Autonomous vehicles

Full vehicle automation cannot be achieved without the streamlining of Advanced Driver Assistance Systems (ADAS). Autonomous vehicles require optimized embedded real-time high-performance processing capabilities to enable the fusion of data from multiple physical sensors. The ability to operate in harsh environments without disruption in the event of internal failures or external events depends on efficient, reliable and secure decision processes. In addition, autonomous vehicles will need to be connected to each other and share information to deliver enhanced operating features and safety to all users.

# Smart manufacturing

By introducing smart devices, machine to machine communication and Cyber-Physical Systems (CPS) into manufacturing processes, the industry will enter a new era. According to German Trade & Invest smart production will become the norm. Systems and devices will exchange and respond to information to manage industrial production processes. CPS do more than just automate production; they transform production tools into decentralized smart factories. The smart factory will change value chains and business models by processing information and making coherent and trustworthy decisions in real-time, operating automated and distributed machines, and communicating with high-level applications in a multi-site and multi-stakeholder environment.

# A pioneering position

CEA Tech institutes Leti and List are combining their long-standing expertise in integrated circuit design and embedded software development to add competitive differentiation to their R&D partners' products. With broad know-how covering various market applications, a multidisciplinary team of experts, and state-of-the-art equipment, Leti and List are capable of seeing the big picture, crossing technological barriers, and exploring innovative solutions.

# Develop appropriate computing solutions

Exponential growth of data (both in quantity and processing power) and computing migration toward cloud-based and embedded systems are spurring the development of new ways of processing relevant information across the communications chain. Today's ultra-low-power computing node, micro-server, and server architectures and cutting-edge computing paradigms demand advanced technologies and an appropriate software environment.

# Innovate energy-efficient connectivity

Two major trends are shaping today's communications systems: low power and integrated technologies. High data rates and versatility, attributes usually found in infrastructures, are now also expected from terminal nodes. Therefore, high-data-rate mobile communications and low-data-rate loT devices share common technological goals. In addition, middleware will also be required to ensure responsiveness despite the heterogeneous nature of the loT.

# Improve sensor capabilities

Whatever the physical measurement—light, sound, pressure, gas—, sensors must be able to produce and transmit relevant, structured data. Sensors must be low-power, wireless, adaptive, cognitive, and multidimensional. Imagers will also be expected to roll in capabilities like High Dynamic Range (HDR) and be highly sensitive and robust enough to withstand harsh environments. Innovations in both hardware and software are needed to respond to these current and future constraints.

# Establish trust

The implementation of cyber-physical systems will require enhanced security to protect privacy and property, ensure the safety of systems, and guarantee the reliability of their components. Smart embedded systems' capabilities must now include troubleshooting, critical control, and security. The challenge is to implement these features while mitigating system overload and over-dimensioning and controlling costs. Profound changes in hardware and software architectures are the only way to overcome these hurdles.

# Effectively partition hardware and software

Development time lengthening, over-engineered hardware, or conservative choices could be the consequences of the increasing embedded systems' and servers' complexity. CEA Tech uses system-level formal analysis to paint a detailed picture of the appropriate hardware-software coupling options, and guides effective architecture choices: the first step to emulating a dedicated hardware-software platform or simply determining the best off-the-shelf platform.

With a broad range of smart physical systems expertise, CEA Tech can identify areas for improvement and help create new business opportunities.

### Highly efficient data processing and quality of service for connected devices

# **Computing** solutions

Based on more than 25 years of experience in the design of application-oriented computing solutions, CEA Tech investigates and develops energy-efficient, high-performance architectures for servers, micro-servers and smart computing nodes. Initially focused on image processing and telecom applications, CEA Tech's expertise has expanded to a broad range of applications in high performance real time computing where the emphasis is on ultra-low power, low latency, and high reliability and dependability. CEA Tech now offers a unique set of silicon-proven digital IPs designed using the most recent libraries (including FDSOI, down to 22 nm).

# on réduites par l'utilisation du FDSOI ion de Back Plane ces par boost de fréquence (FBB) ou 1- Gate stack High k (Cox 21) 3- Si-film (=L<sub>G</sub>/3) Metal-Gate (V<sub>7</sub>) No channel doping No pocket implant 2- Raised SD (RSD 5)

# Developing ultra-low power computing computing paradigms computing nodes

To tackle the challenges of efficient IoT & CPS computing nodes, CEA Tech designs high performance, very-low power and reconfigurable architectures. Researchers have developed specifically-optimized IPs with low latency, dedicated memory management, and a high level of determinism for critical applications and image processing.

All of our innovations are implemented under the L-IoT™ initiative.

# Designing servers, micro-servers & gateways

All aggregated data must be sent to the Cloud for processing without compromising confidentiality. Joint hardware and software development maximizes parallelism with high energy-efficiency, taking advantage of both state-of-the-art processing (ARM 32-64-bits, MIPS, RISC-V, etc.) and advanced IPs (system management, high speed optical transmission, near memory processing).

Thanks to in-depth knowledge of integration technologies, CEA Tech leverages a unique methodology combining multicore architectures made of 3D integrated ICs called "chiplets," taking advantage of modularity to increase scalability, reuse, and computing power while keeping design and fabrication costs

# Adding new

Processing massive volumes of data is driving the need for new computing paradigms to increase speed and energy efficiency. CEA Tech set up a framework for the exploration, implementation, and synthesis of various Deep Neural Network (DNN) topologies and models, enabling major productivity gains in DNNs of several million neurons. This framework can generate code directly for various CPU. GPU. or dedicated accelerators using classical digital coding or «spike-based» encoding. Neuromorphic computing, quantum computing... are examples of new computing paradigms explored by CEA Tech.

# Facilitating application development

Complex systems must be implemented on Ultra-Low Power nodes as well as servers infrastructures without compromising data security and integrity. CEA Tech has developed new standards-compliant methods. middleware, hypervisors and execution environments to efficiently implement an application and supervise its execution under various constraints (real-time, heat dissipation, uptime). As an example, a patented multicore execution model guarantees service quality at node and system levels.

asynchronous multi-core processor

performance processing

FPGA based board for Deep Neural Network implementation

# Wireless connectivity

Reliable & energy-efficient wireless communication

With more than 15 years of experience in communication technologies, CEA Tech is well positioned to develop complete System-on-Chip (SoC) solutions. From architecture analysis to IC design and industrial testing, CEA Tech's SoC capabilities encompass transceiver integration, digital processing, microcontrollers, memory, low-power management, auto-calibration and control loops, and built-in self-testing—all on a single chip. Addressing ultra-low-power as well as high data-rate markets, CEA Tech's experience covers low-frequency to sub-Terahertz band applications and silicon photonic solutions. At the middleware level, CEA Tech can make innovative recommendations to ensure the abstraction of distributed and heterogeneous nodes on communication networks.

# Innovating connectivity for IoT

The IoT is driving advances in communication systems, generating new needs such as versatile radios. CEA Tech is innovating by combining ultralow-power wake-up and on-demand high-data-rate wireless systems with smart power management including energy harvesting. Ultra-wideband technology is also a major R&D topic that CEA Tech is addressing to develop accurate indoor location systems. These innovations in ULP connectivity and computing are implemented under the L-IoT™ initiative.

# Enabling 5G highspeed mmW communication

CEA Tech is preparing for tomorrow's need for low-cost, high-data-rate millimeter-wave communications. Developments include solutions for short-distance Gigabyte/s links at several tens of GHz using standard silicon technologies. CEA Tech is currently working on sub-THz circuits for communications and imagers.

# Building multiband power RF FEM < 6GHz

Front-end modules are becoming a critical element in 4G–5G cellular communications, due to the increasing number of bands of operation, new deployment scenarios, dynamic variations in physical channels, and smaller antenna form factors. CEA Tech designs power amplifiers, acoustic filters, matching networks, and antenna switches, for innovative, highly integrated and reconfigurable solutions.

# Creating high performance integrated solutions

With particularly stringent specifications, Professional Mobile Radio is unique segment on the mobile communications market. CEA Tech brings breakthrough opportunities in analog signal processing, to innovate effective integration solutions, always in close collaboration with our industrial R&D partners.

# Developing middleware for sensor data mining

From factory automation to smart cities, Cyber-Physical Systems are made up of a broad range of heterogeneous subsystems interacting in complex scenarios. CEA Tech has developed two kinds of middleware to ensure that these systems behave homogeneously from an application point of view: SENSINACT is Java-oriented and dedicated to smartcity application deployment; LINC is a tool for building functional robustness and causality in distributed automation systems.

RF/digital chip for wireless communication

# 101010 101010

# **Smart** sensors

Making the leap from physical information to data interpretation Imagers and many other physical sensors now require built-in processing capabilities. CEA Tech combines know-how from a variety of disciplines, taking a unique co-design approach that simultaneously addresses sensor, readout circuit, and signal processing. This results in innovative solutions that cut across physics, electronics, and automation systems. Sensors benefit from local processing and embedded software, and can adapt dynamically to the environment by performing dynamic matching to their region of interest. CEA Tech's innovative solutions also support multi-sensor data fusion techniques. These capabilities are crucial to producing efficient, multidimensional, and high value information.

# Developing embedded sensor architectures

Power consumption is a major challenge for embedded sensors. CEA Tech develops dynamic and cognitive architectures that perform in ultra-low (or even zero) power consumption modes. With external and internal wake-up modes, sensors can adjust consumption automatically to system needs. They can also modulate data rates and manage communication channels to increase energy efficiency. And, when coupled with energy harvesting systems or remote power blocks, sensors can even be self-powering.

# Adding smart processing capabilities

Pre-processing is a required step for the development of dynamic region of interest matching and reducing complex-sensor latency. CEA Tech leverages 3D silicon integration techniques to assemble dedicated signal processors with sensors as close to the signal sources as possible. This advanced technique enhances event detection, data optimization and compression, efficient data fusion as well as memory management. Multi-physical and heterogeneous sensor data fusion software further contributes to data interpretation and system relevance.

# Delivering high precision when needed

To achieve extraordinary levels of sensitivity, very-low-noise analog architectures and high-dynamic range analog-to-digital converters are required. CEA Tech develops integrated circuits that attain less than 1 electron noise, low nV/VHz thresholds and 16-bit-resolution converters with few femto joules per quantification step. The performance of these readout circuits has been demonstrated on a wide range of imagers, from infrared to X-ray and

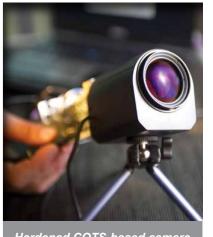

# Guaranteeing robust performance in harsh environments

Oil & gas exploration, aircraft wing and engine monitoring, and civil nuclear applications all require specific sensor designs that combine secure, reliable, and robust software with hardened technologies and architectures. Sensors for these applications must be able to tolerate high pressure, high voltage, high temperature, and, in some cases, exposure to radiation.

for human detection

Hardened COTS-based camera for nuclear power plants

# Security and safety for digital trust

Building safe. secure electronic systems in an open, distributed. and fully-connected world Preventing cyber-attacks, identity theft, interference between applications, and unexpected or faulty behaviors add to system cost. Digital trust challenges represent a threat to IoT and CPS market growth. With more than 25 years of experience in trustworthy systems design, 20 years in radiation-hardened systems, and 10 years in reflectometry signal processing for automotive & avionics applications, CEA Tech has the expertise to make embedded systems safer and more secure while ensuring application performance, and reducing cost and form factor. CEA Tech develops hardware and software solutions enabling the widespread adoption of smart devices and embedded servers with the digital trust guarantee.

# acces securise

# Monitoring, diagnosis and prediction

CEA Tech has developed an innovative algorithm to detect and locate faults in complex cable harnesses. Embedded in an ASIC, the algorithm significantly reduces maintenance costs.

An off-the-shelf component (COTS) radiation characterization methodology and system design know-how based on these components, enables the use of integrated components in extreme environments.

Because semiconductor reliability decreases with miniaturization, CEA Tech has developed mathematical models and software tools to manage design risks and architecture specifications for maximum reliability.

CEA Tech also offers a vast portfolio of hardware and software IPs that can be inserted in an existing SoC to dynamically control voltage levels depending on the system's performance requirements while guaranteeing a failure rate level.

# Developing deterministic, real-time, and mixed-critical systems

CEA Tech researchers bring 25 years of unrivalled know-how in the design of time-triggered OS (RTOS) for nuclear and automotive applications. This background-and the rigorous stateof-the-art RTOS analysis—leverages the development of methodologies and tools to determine the best application based operating system, and to cointegrate safety-critical and highperformance applications in distributed and many-core systems under temporal determinism and real-time requirements.

# Secure computing: confidentiality & integrity

Industrial Supervisory Control And Data Acquisition (SCADA) systems, which are now connected to the internet, can be protected through a highly-secure low level hypervisor developed by CEA Tech. This guard enforces security such that even a severe attack like privilege escalation could not bypass this protection.

Based on efficient homomorphic encryption, CEA Tech has developed a unique software toolchain. Applications are now capable of encrypted data processing, without the need to decipher it. Data processing in the cloud is protected from potential security breaches end to end.

CEA Tech also develops the key technologies for embedded systems protection, such as dynamic and polymorphic compilation to ensure physical signature randomization of an embedded application.

# Hardware-Software methodologies integration

Meeting manufacturers' product dimensioning, prototyping, testing, and demonstrator needs CEA Tech can efficiently guide companies along their complex hardware-software design processes. We can identify code bottlenecks, increase software speed, determine criticality, conduct real-time analysis, assess non-functional properties, co-design specific hardware-software, target off-the-shelf components (CPU, GPU, FPGA, DSP), provide options to merge digital models and physical process models, and provide dedicated tool development to support design methodologies. CEA Tech's Leti also runs the Silicon Impulse program which promotes the FD-SOI ecosystem.

# Applicationdriven hardware platform

CEA Tech offers resources for analyzing a wide range of hardware-software solutions - for parallel processing and real time operation to its R&D partners. CEA Tech optimizes hardware-software co-design to achieve the highest possible performance while also meeting real-time computing, high data rates, standards, and qualification requirements.

Sequential code analysis, automatic code transformation, parallel machine mapping, performance prediction and specifications for appropriate programming models are investigated. Software runtimes are drastically reduced and hardware porting costs are optimized.

# Design space exploration

With powerful hardware emulation tools, a full EDA suite, and a proprietary virtual platform, CEA provides unrivalled architecture exploration and simulation services. R&D partners benefit from early-stage exploration, hardware-software partitioning, and virtual prototyping support provided in a unique environment. Ultra-fast simulation and emulation tools accelerate design and pinpoint problems. SoC, OS, and applications can be tested before any hardware is produced.

# SoC Test

Our lab includes an industrial-grade digital, mixed-signal, and RF test system, a 300 mm full-automated wafer prober and a high throughput packaged circuit handler. Temperature range is controlled from -60 °C to 300 °C. Advanced know-how in Built-In-Self-Test design and research in statistical analysis shorten test times.

# Silicon Impulse

Silicon Impulse is a one-stop shop for IC development on advanced technologies, for prototyping and low volume production. Our partners can access the program to reduce their learning curve for adopting FDSOI. Unique in Europe, CEA Tech's Leti and List, offer businesses consulting services, easy access to ultra-low power FDSOI, architecture emulation, design know-how in mixed-signal and RF ICs; a broad selection of generic, commercial, and proprietary IPs; testing and validation of small production runs. At the completion of the project production is transferred to our partner's supply chain of choice.

# **CPS Impulse**

CPS Impulse is an innovative solution for Cyber Physical Systems development offered by CEA Tech to enable its industrial partners to develop advanced embedded systems covering every aspect of design constraints: Cost, area/size, power, performance, reliability, security and dependability. Sophisticated virtual prototyping, neural network design, parallel architecture benchmarking tools as well as optimized off-the-shelf software components such as neural network accelerators, sensor fusion blocks and middleware for sensor networks are but a few examples of solutions available.

# **Advanced** demonstrators

STELLAR is a versatile parallel architecture offering high performance & high energy efficiency, for mixed-critical transport applications

On 28nm FDSOI, a 4-core STELLAR reaches 3.2 Gops at 800 MHz for less than 1W.

Targeting mixed-critical transport applications (autonomous vehicles, avionics), the STELLAR architecture supports advanced reliable and deterministic features, for dependable execution.

STELLAR combines in a single SoC the high energy efficiency brought by low complexity Rocket cores with the unrivalled computing power brought by out-of-order BOOM cores. The architecture provides smart heterogeneity and energy consumption management services, to efficiently benefit from each core's assets.

STELLAR also provides a powerful infrastructure that eases third-party's IPs integration. Customized STELLAR architecture and its dedicated software are rapidly evaluated by hardware emulation, ensuring low cost validation and fast time-to-market.

Ultra-Low Power & Very High Performance capability on a single

28nm FDSOI SoC for IoT.

Liot

Developed

on FDSOI

technology,

L-IoT™

architecture

combines best

CEA Tech

expertise to

support

Ultra-Low

Power IoT

requirements

L-IoT™ architecture is developed to demonstrate benefits of hardware-software & mixed-signal co-design, and support various Ultra-Low Power scenarios for IoT applications.

FDSOI 28nm brings very high performance modulation with an efficient use of Back-Biasing. Innovative analog and digital blocks in sensing, imaging, wireless communication, power management, processors and accelerators are developed. And a flexible Always-responsive/On-demand architecture is proposed with advanced very low energy cost wake-up design.

L-IoT™ combines many innovative IP blocks in technology, design, architecture, and embedded software. Some of them are already available to improve our future partners' IoT systems.

### NEURO **COMPUTING**

N2D2 framework assists in DNN exploration & generation, and selects the right COTS to fit with industrial constraints. Pneuro is a multipurpose energy optimized accelerator for DNN. Performances on video FPGA are compared to Quad-ARM A7. They explode with ASIC portage.

speed energy

### 3D-NOC **INTEGRATED CIRCUIT**

3D-NOC is a 3D heterogeneous multi-core IC. Silicon-proven communication IP blocks are now available for any 3D IC product design, including in-house 3D Network-on-Chip, robust and easy to integrate asynchronous 3D links between processors.

0.32 pJ per bit with multi-core 3D-NOC IP

### **POWER OPTIMIZATION** THROUGH VOLTAGE SCALING

No additional test time, less than 5% of area overhead. On advanced technology nodes, a voltage scaling technology has been developed to optimize margin on each IC in order to reduce its power consumption without generating faults. Demonstration on 28nm FDŠOI.

POWER savings

### **FOXY**

Foxy is a low cost and Ultra-Low Power RF transceiver for Ultra-Narrow Band applications, fully compatible with SIGFOX sensor nodes. This mixedsignal SoC has a very long battery life thanks to a very low leakage current.

**ULP RF SIGFOX** compatible

### **G-LINK**

G-Link is a low-power wireless connection that enables instantaneous data transfer in the gigabit range between two devices a few centimeters apart. Implemented in a very low cost IC, high data rate short range video transfer was demonstrated at the CES Show in Las Vegas.

60GHz 2.5Gbps 100mW

### **ΣFUSION**

∑fusion is a low power real time sensor fusion processing system of LIDAR data for autonomous car applications. Application was ported on a 900MHz ARM Cortex A9, and compared to state-of-the-art algorithms on Intel Core I5.

energy

An electronic retina enables smart independent and local image processing. A 3D-stacked technology allows embedded digital processing, higher density, lower consumption and better feedback between analog and digital layers.

1000 op./pixel@ FRAMES/SEC

### PRESSURE MEASUREMENT **RIBBON**

This high density 16-bit pressure measurement ribbon with 10-bit thermal compensation for air-flow characterization consists of 128 independent channels at a 4.5mm pitch. Over a 20kPa-95kPa range (-30°C/+60°C) it reaches only 24Pa global system noise on a 100Hz pressure bandwidth.

### **LOW NOISE IMAGE SENSOR**

A sub-0.5 e-rms temporal read noise VGA image sensor was integrated in a standard 0.18µm 4PM CMOS process. The low noise performance is achieved exclusively through circuit optimization without any process refinements.

**RMS NOISE** 6.5<sub>µm</sub>

pitch, 4T pixel

### **SAFETY & MANYCORE**

Safety-critical engine control applications and data-intensive processing are executed in a 256-core processor for an avionics partner. Both applications share same hardware resources concurrently while interference is successfully prevented.

**PREVENTED** interference **PERFORMANCE** on demand

### **CABLE DIAGNOSIS**

This ASIC enables wire defect detection and location within reduced footprint, power consumption and cost. This paves the way to constant monitoring of complex wiring networks in various domains, such as aeronautics or automotive.

**LOCATION ACCURACY** of cable length

# CEA Tech **Platforms**

A unique "critical mass" of world-class experts and equipment resource to drive innovation for business.

### THE ONLY DESIGN CENTER OF ITS KIND IN EUROPE

The SoC design platform is one of Europe's leading technological research centers specializing in digital, analog, mixed-signal and radiofrequency component design.

The components developed in the design center target lower power consumption, lower noise and higher performance than commercially available circuits, making them ideal for demanding applications such as avionics, automotive, healthcare and IoT.

The platform uses advanced emulation and simulation techniques to predict insystem component behavior from the planning phase and delivers fully functional silicon through the prototyping stage. The design center also collaborates with its industrial partners to combine its innovative functional blocks stemming from its own R&D work with existing circuits to deliver highly differentiated solutions. The platform has access to many advanced semiconductor processes such as 28 nm and 22 nm FD-SOI or 55 nm and 40 nm RF-SOI through its fab partners.

The platform's Silicon Impulse full service design center delivers highly complex SoCs to systems integrators, OEMs and fabless semiconductor manufacturers alike.

Full EDA toolchain including physical design and verification, Advantest V93000 SoC test system, Mentor Graphics Veloce 2 emulator and a rich set of foundation and complex IP libraries.

LOCATION

# Embedded Systems Design Platform

### OVERCOMING THE CHALLENGES OF HARDWARE-SOFTWARE INTEGRATION

The embedded systems design platform offers unrivalled know-how in hardware-software integration.

The platform supports the development of systems that target high reliability and security demands for big data servers, IoT devices, transportation, energy and manufacturing functions. The R&D conducted at the platform covers two

- Hardware and software partitioning to optimize system design and integration.

- Integrating electronic sub-systems or modules into existing systems.

Both types of R&D share the objective of enhancing overall system performance through the use of smaller form factors, less memory, better energy efficiency, lower cost and greater security and reliability.

The platform's advanced simulation resources are used to validate target systems in environments representative of the applications in which they will perform. This unique capability to simultaneously address the design and the final specifications of the target application has attracted more than 40 industrial partners of all sizes.

## **KEY EQUIPMENT**

CAD tools for hardware and software simulation, Synopsys ZeBu High perf SoC emulation system, FPGA based prototyping, test benches replicating severe environments (high temperature, radiation, etc.)

LOCATION

List (Paris-Saclay)

List, Smart digital systems

Commissariat à l'énergie atomique

et aux énergies alternatives

CEA Saclay Nano-INNOV |

Bât. 862, PC 172

91191 GIF-SUR-YVETTE CEDEX | FRANCE

+33 169 084 967

Leti, technology research institute

Commissariat à l'énergie atomique

et aux énergies alternatives

Minatec Campus |

17 rue des Martyrs

38054 GRENOBLE CEDEX 9 | FRANCE

+33 438 783 729

www.leti.fr

For further information, please email contact.dacle@cea.fr

www-list.cea.fr

Photos: F. Ardito, A. Balazh, CEA, DELPHI, FOTOLIA, Iurii, P. Jaquet, P. Jayet, Leti, List, Maxsattanna, MC David, S.Pajaniradja, RA2 Studio, SHUTTERSTOCK, P. Stroppa, B. Truong